智宇物聯(lián) 專注于提供高穩(wěn)定、高速率的三網物聯(lián)網卡

林芝地芯片技術被「卡脖子」?這是中國對抗封鎖最有效的「武器」

- 作者:智宇物聯(lián)

- 發(fā)表時間:2022年10月17日

- 來源:智宇物聯(lián)

2010年的夏天,伯克利大學的研究團隊嘗試設計和開發(fā)一套完整的新指令集。四年后,RISC-V問世。

從最初的多方質疑,到逐漸獲得學術圈、芯片和系統(tǒng)公司以及政策的認可和重視,近年來業(yè)界對于RISC-V的態(tài)度發(fā)生了180度的轉變。

在中國芯片核心技術被「卡脖子」的當下,RISC-V將成為中國與美國封鎖技術政策對抗最有效的技術武器。

它被行業(yè)給予重托,被視為中國未來十年里最具潛力的芯片平臺,大有超越ARM之勢。

撰文 | 四月

ARM架構 和 RISC-V架構都源自1980年代的精簡指令計算機RISC,正如上世紀末的Windows和Linux之爭。

PC時代成就了x86,移動互聯(lián)網時代ARM是絕對的主流。

但在物聯(lián)網和AI時代的新興領域,RISC-V和ARM正處于同一起跑線上,RISC-V憑著指令集開源、簡潔等特性很有可能可以擊敗ARM,或者至少能夠占據可觀的市場份額。

更為重要的是,在芯片核心架構技術被「卡脖子」的當下,RISC-V將成為中國與美國封鎖技術政策對抗最有效的武器。

機器之心消息,RISC-V芯片設計公司芯啟科技日前在北京發(fā)布三款國產CPU IP產品,并同時對外開源,以促進國內RISC-V芯片的產業(yè)發(fā)展。

發(fā)布活動由中關村芯園聯(lián)合北京芯啟、中國RISC-V產業(yè)聯(lián)盟(CRVIC)共同舉辦,在產品發(fā)布之余,各方還積極探討了基于RISC-V技術架構的應用發(fā)展方向和創(chuàng)新設計思路,RISC-V的工程經驗以及在AI芯片設計中的經驗等話題。

1 爆發(fā)式機遇

隨著美國對中興、華為等中國IT命脈企業(yè)立下重重技術鐵幕,一時間國內輿論大嘩。越來越多的產業(yè)人士意識到:

以美國為代表的發(fā)達國家正在通過高附加值產業(yè)進行產業(yè)壟斷,以ARM、Synopsys、Cadence等為代表的知識產權交易商,通過苛刻的知識產權授權規(guī)則已經阻礙并減緩我國集成電路設計商的技術創(chuàng)新與產業(yè)的發(fā)展速度。

所謂中國「自主研發(fā)」的芯片技術,到了關鍵時刻卻實實在在地被人卡著脖子。

如何利用好更為強大和開發(fā)的技術武器與之長期有效對抗,成為擺在我國集成電路從業(yè)者面前必須面對的重大問題。

談到芯片的「自主可控」,最為關鍵的技術在于芯片指令集架構,通常簡稱為「芯片架構」。它是溝通軟硬件運算之間的橋梁,是核心基礎軟硬件生態(tài)系統(tǒng)的基石,其重要性不言而喻。

在半導體行業(yè)的歷史上,曾出現過諸多的架構,但隨著時間推移和市場競爭,類似于MIPS等架構已經逐漸退出舞臺。目前主流的架構包括Intel的X86、ARM架構,在日常生活中見到最多的是ARM,基本上所有的芯片公司都在采用ARM的架構。

談到物聯(lián)網應用已經不能繞開ARM,但是在ARM基本上要一統(tǒng)天下,甚至侵入Intel的桌面PC和服務器業(yè)務的時候,免費開源的RISC-V誕生了。

RISC-V是一種免費開源指令集架構(ISA)。由加州伯克利分校的研究團隊開發(fā)與公布,于2011年5月正式發(fā)布第一版。該指令集設計非常簡單,采用了基礎指令集與擴展指令集的方式,基礎指令集只包含了不到50條指令。

「RISC-V可能真正能成為國產的自主的指令集架構。」RISC-V推廣人,武漢聚芯微電子架構師胡振波在接受媒體采訪時談道,RISC-V作為免費的架構,將會和ARM產生競爭。在手機等傳統(tǒng)ARM的壟斷領域會保持強勢存在,在一些新興的邊緣領域,比如IoT、AI、邊緣計算領域,RISC-V將具有爆發(fā)空間。

「中國未來十年都會去全力支持這個技術」,品利基金半導體行業(yè)投資經理陳啟向機器之心表示。這被行業(yè)視為最具潛力的芯片平臺,大有超越ARM之勢。

歷經八年時間發(fā)展,RISC-V指令集「朋友圈」已經逐步吸收到大量具備影響力的企業(yè)。2015年非盈利組織RISC-V基金會成立,旨在凝聚全世界力量構建開放社區(qū),推廣RISC-V架構。

迄今已有100多個機構加入,包括谷歌、華為、IBM、阿里巴巴、英偉達、高通、三星等企業(yè),以及加州大學伯克利分校、麻省理工學院以及中科院計算所等學術機構。

此外,美國之外的產業(yè)界和國家也在積極備戰(zhàn)RISC-V技術。全球第一大硬盤產商西部數據宣布將把每年各類存儲產品中嵌入的10億個處理器核換成RISC-V;印度將它作為事實國家指令集,以色列國家創(chuàng)新局選擇基于RISC-V研制為全國企業(yè)服務的處理平臺。

去年,我國發(fā)布了首個RISC-V支持政策并成立了中國RISC-V產業(yè)聯(lián)盟。上周,清華和伯克利共同發(fā)起RISC-V國際開源實驗室,由圖靈獎David Patterson教授牽頭。

相對于ARM和x86,RISC-V強調開源和成本優(yōu)勢,并以簡單可擴展的指令集提供更高效的硬件。不過,RISC-V想要全方位進軍芯片市場,與ARM以及x86分庭抗禮,其背后的生態(tài)建設尤為關鍵,這也是當前RISC-V中國化面臨的最大問題之一。

2 對標ARM Cortex和NVDLA

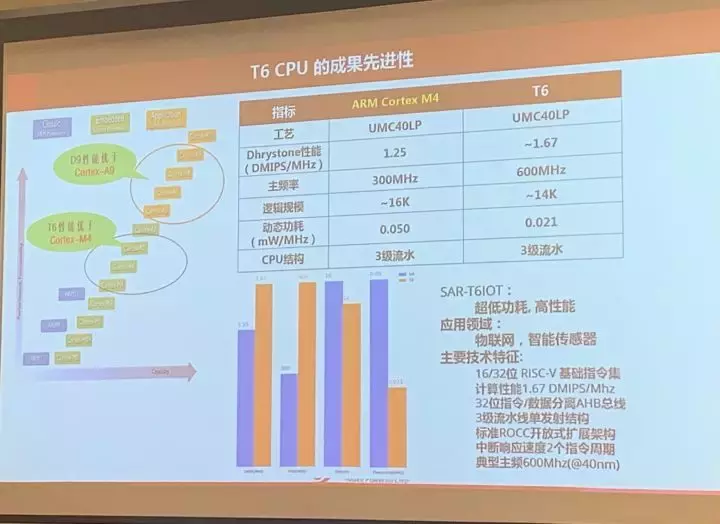

芯啟此次開源的三顆IP為SAR-T6系列、SAR-D9系列和TNA-300,分別對標ARM Cortex-M4、ARM Cortex-A9和英偉達的開源神經網絡加速器NVDLA。

- SAR-T6系列對標ARM Cortex-M4,面向AIoT終端、傳感器、機電MCU、輕量級智能以及眾核智能應用。

- SAR-D9系列對標ARM Cortex-A9,面向醫(yī)療、通訊、工控、機電MCU、視頻音頻處理、輕量級智能、通用算法加速場景。

- TNA-300對標英偉達的開源神經網絡加速器NVDLA,面向設備端AI方案。

芯啟科技團隊核心成員在芯片設計領域平均工作經驗超過15年。研發(fā)成員來自于985、211重點大學的相關專業(yè),并曾長期任職于華為等國內著名軟硬件公司重要崗位。

目前,公司采用CPU 軟硬核 IP 授權的商業(yè)模式,提供嵌入式 CPU 指令設計、體系結構設計、超大規(guī)模集成電路設計、軟件編譯器及工具鏈設計、系統(tǒng)芯片平臺設計等服務,同時自產一系列嵌入式 CPU核產品。

據介紹,芯啟基于改良后的RISC-V架構CPU IP 的主要亮點包括:

1、全自主可控:開源指令集RISC-V,支持客戶自主定義;微架構自主,完全自行開發(fā),客戶可通過技術服務深度定制和修改。

2、硅成本更低(50%-70%)。

3、性能更優(yōu),提升20%。

4、提供設計的完全自由度。硬件方面包括指令集、微架構、片上架構,工具鏈包括編譯工具鏈、開發(fā)調試工具鏈、SDK環(huán)境,軟件包括OS移植性等。

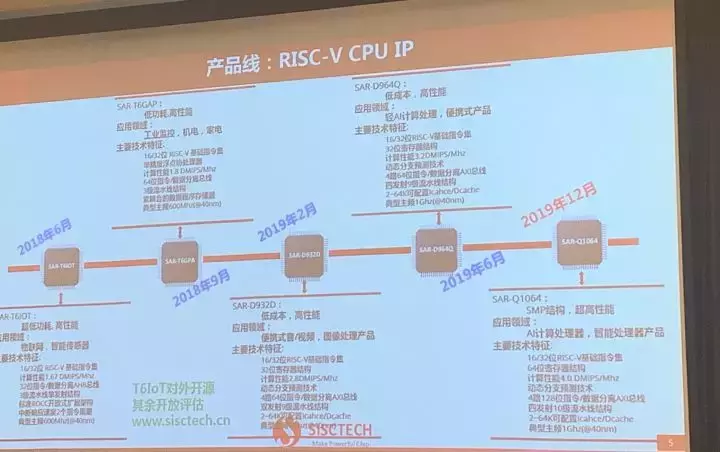

具體來看,三顆芯片的主要性能包括:

- 1)SAR-T6IoT系列強調超低功耗、高性能,16/32位RISC-V基礎指令集,40nm工藝,針對物聯(lián)網、智能傳感器等場景,中斷響應速度2個指令周期,典型主頻600Mhz,計算性能達到1.67 DMIPS/Mhz,采用32位指令/數據分離總線,三級流水線單發(fā)射架構。

- 2)SAR-T6GPA系列強調低功耗、高性能,采用單精度浮點協(xié)處理器+緊耦合的數據程序存儲器結構,16/32位RISC-V基礎指令集,40nm工藝,針對工業(yè)監(jiān)控、機電、家電等場景,采用三級流水線架構,典型主頻600Mhz,64位指令/數據分離總線,計算性能達到1.8 DMIPS/Mhz。

- 3)SAR-D932D系列強調低成本、高性能,采用32位寄存器結構,16/32位RISC-V基礎指令集,40nm工藝,針對便攜式音/視頻,圖像處理產品,采用雙發(fā)射9級流水線結構,動態(tài)預分支預測技術,4路64位指令/數據分離總線,計算性能達到2.8 DMIPS/Mhz,2-64K可配置Icahce/DTCM。

在今年底,芯啟還計劃推出SAR-Q1064 AI芯片,強調超高性能,適用于智能處理器產品。

SAR-Q1064采用64位寄存器結構,16/32位RISC-V基礎指令集,計算性能達到4.0 DMIPS/Mhz。采用SMP架構,動態(tài)分支預測技術,4路128位指令/數據分離總線,采用四分射10級流水線結構,2-64K可配置Icahce/Dcache,典型主頻1GHz。

上述四款芯片均選擇40nm工藝,芯啟方面表述,主要為了在成本可控的情況下將性能優(yōu)勢潛力發(fā)揮到最優(yōu)。

芯啟的開源方式包括兩種,一種是通過與中關村芯園的國產IP應用服務平臺合作,通過平臺將國產CPU IP及對應設計服務向產業(yè)輸出。活動現場,芯啟科技與中關村芯園的國產IP應用服務平臺正式簽署了合作協(xié)議。

與此同時,中關村芯園的國產IP應用服務平臺開啟面向芯片設計用戶的支持計劃,承諾提供0元授權、完備IP技術交付和可擴展的技術服務支撐。芯啟作為RISC-V架構領域首批提供技術支持的企業(yè),加入到芯園的服務鏈條中。

這里簡單介紹中關村芯園公司背景,對于半導體產業(yè)人士而言不失為一個備選的合作伙伴。芯園由中關村發(fā)展集團作為控股股東組建,作為國家集成電路設計北京產業(yè)化基地,其服務和業(yè)務具備一定的公益性質。

公司圍繞集成電路設計,為企業(yè)提供EDA License租賃、IP評估與授權、生產流片(MPW、工程批、批量生產)、封裝測試代理、IC人才培訓、芯片應用等全產業(yè)鏈的公共技術服務支撐。

IP開源的第二種方式則是通過芯啟科技官網獲得開源資料包。目前,超低功耗版本T6 IoT設計已經在芯啟網站實現開源,其余設計開放評估,網址為。

3 基于RISC-V的AI芯片如何開發(fā)?

RISC-V在處理器領域堪稱「歷史上最為徹底的」 開放程度,「大道至簡」被視為RISC-V架構之魂,架構短小精悍。

「能屈能伸」是RISC-V指令集的最大特性,相比其他成熟的商業(yè)架構,RISC-V最大一個不同在于它是一個模塊化的架構。不同的部分以模塊化的方式組織在一起,從而試圖通過一套統(tǒng)一的架構滿足各種不同的應用。

這種模塊化是x86與ARM架構所不具備的。

以ARM的架構為例,ARM的架構分為A、R和M三個系列,分別針對于Application(應用操作系統(tǒng))、Real-Time(實時)和Embedded(嵌入式)三個領域,彼此之間并不兼容。但是,模塊化的RISC-V架構能夠使得用戶能夠靈活選擇不同的模塊組合,以滿足不同的應用場景。

雖然RISC-V看上去已經是「老少咸宜」,但要真正將其產業(yè)化和產品化,仍然有不少坑要淌。

芯啟科技聯(lián)合創(chuàng)始人、總經理楊旭光向機器之心簡單回顧了團隊在RISC-V的研發(fā)歷程。在2015年,首先基于RISC-V展開研發(fā)布局,2016年初基于RISC-V為公安等政企客戶提供了定制的安全芯片設計并進行了流片,成功交付客戶完成驗收。

在設計與研發(fā)初期,芯啟面對GitHub上的上百個開源工程版本的選擇有些迷茫。

不同開源工程意味著可能對應的是不同的開發(fā)語言,每個版本又有不同的分支,每個分支每天還面臨著大量更新,如何找到適合自己的版本,以及如何跟進版本更新成為關鍵。

最初,芯啟選擇了伯克利的Rocket工程版本,采用Chisel語言編寫,其特點在于抽象靈活,代碼量小,維護簡單,可以自己造類庫和擴充功能。

但同時也存在其缺點,通讀性差,可交付性差,工程化應用還不成熟。這種語言適合在設計前期階段快速探索,不太適合在工程中使用。類似地,BOOM工程也適合研究使用,也不太適合工程化。

經過早期的探索和學習,以RISC-V標準為源頭,吸收RISC-V的模塊化理念,2017年團隊開始開始選擇自主創(chuàng)新,反思傳統(tǒng)RISC-V架構中的10多處不足進行迭代革新。

近兩年,團隊基于對RISC-V CPU開源架構的消化、吸收和創(chuàng)新,形成了芯啟科技完全自主可控的嵌入式CPU技術積累,可以靈活的根據需求對指令集和微架構進行增刪裁剪,全面掌握了嵌入式CPU發(fā)展的主動權,推出了完全自主可控的系列CPU產品。

同時,公司在AI領域發(fā)力,推出了完全自主可控的AI加速引擎,全力助力傳統(tǒng)產業(yè)的AI賦能升級。

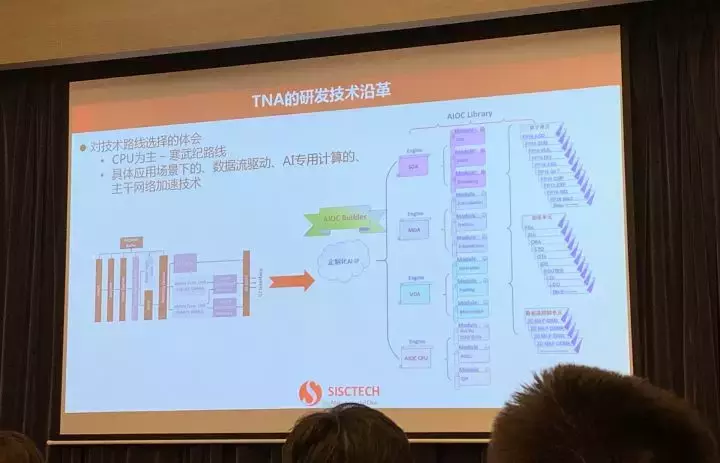

據介紹,芯啟TNA(Tiny Neutral Network Accelerator) AI處理器架構的研發(fā)思路包括兩個層面:

- 一是自主掌握主要核心,實現用RISC-V替代ARM,用多種專用加速引擎組成,實現AI處理加速;

- 二是開展嵌入式優(yōu)化,打開「專精」方向,以RISC-V協(xié)調并行調配,提升AI算力投射和適配算法的靈活性,并為面積、成本和功耗做折中。

TNA強調以海量端設備能接受的價格,提供神經網絡、訓練部署、核心芯片、硬件設計、智能功能組合成的「交鑰匙工程」,提供直觀具象的AI功能,工作環(huán)境尊重傳統(tǒng)產品的設計方案與使用習慣,并提供客戶在成本、算力、AI功能等方面的差異化選擇權力。

從基礎做起,內部重新規(guī)范,梳理研發(fā)概念,解決團隊對接問題,包括軟硬件開發(fā)概念對接、算法優(yōu)化研發(fā)目標一致、未來對接客戶需求更加清晰。從底層模塊做起,形成IP和組合IP的自主體系。

依靠團隊在CPU技術方面的技術積累和項目牽引,芯啟目前已經完成了自有深度學習加速模塊設計,并集成進自主CPU指令架構,已經向主流院校和AI廠商輸出相關成果,定制完成支持AI原語計算的指令模塊。

通過四年在RISC-V領域的技術積累,芯啟具備提供大量基于RISC-V標準指令及自定義擴展指令的CPU內核模塊IP的能力。

攝于芯啟辦公室

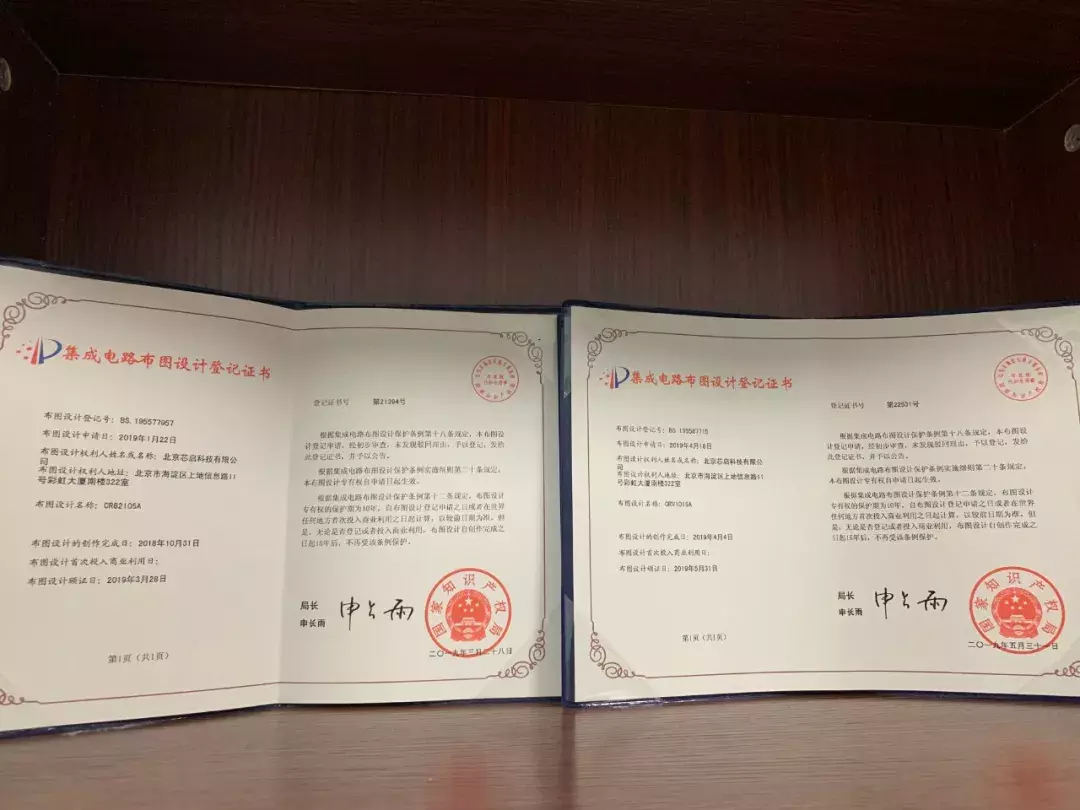

擁有多項關鍵專利技術和自主IP,其中包括CPU IP(SAR-T6、SAR-D9、SAR-Q10),算法協(xié)處理器IP(機器學習算子、張量計算算子)、AI算法加速(卷積、池化、激活、全連接)。

4 三大路徑確保生態(tài)發(fā)展

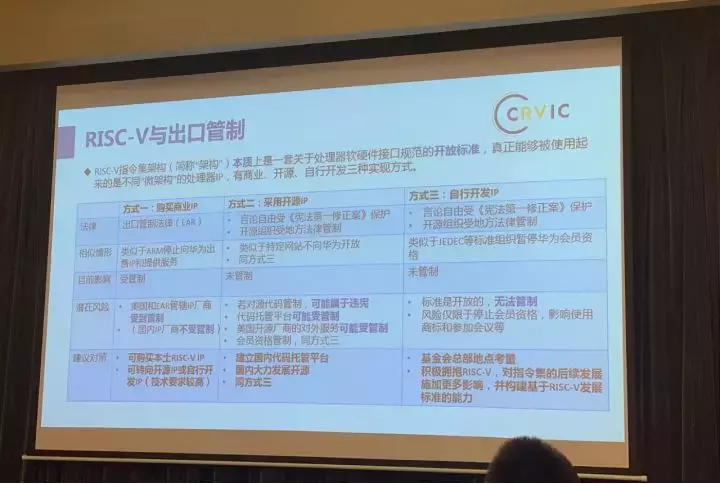

在芯片設計之外,中國RISC-V產業(yè)聯(lián)盟秘書長滕嶺 還分享了RISC-V應用生態(tài)的發(fā)展途徑,以及后續(xù)是否可能受到出口管制的分析。

RISC-V本質是一套關于處理器軟硬件接口規(guī)范的開放標準,真正能夠被使用起來的是不同「微架構」的處理器IP,有商業(yè)、開源、自行開發(fā)三種實現方式。

- 方式一是購買商業(yè)IP,受美國出口管制法律(EAR)的管制,類似于Arm停止向華為出售IP和提供服務。潛在風險是美國和EAR管轄IP廠商收到管制,但國內IP廠商不會受到美國的管制。對于這些風險,對策是可購買本土RISC-V IP,可轉向開源IP或自行開發(fā)IP(技術要求極高)。

- 方式二是采用開源IP,方式三是自行開發(fā)IP,這兩種方式的言論自由受《憲法第一修正案》保護,開源組織受地方法律管制。

- 方式二類似于特定網站不向華為開放以及部分標準組織暫停華為會員資格,目前不受管制。潛在風險是若對源代碼管制可能屬于危險,代碼托管平臺可能受管制,美國開源廠商的對外服務可能受管制,美國開源廠商的對外服務可能受管制,會員資格也可能受到管制。

對于這些風險,有效的的應對策略包括 建立國內代碼托管平臺、國內大力發(fā)展開源和積極擁抱RISC-V。

方式三類似于JEDEC等標準組織暫停華為會員資格,目前未受管制。潛在風險是標準是開放的,無法管制,不過風險僅限于停止會員資格,影響使用商標和參加會議等。

相應對策主要有兩點,一是基金會總部地點考量,二是積極擁抱RISC-V,對指令集的后續(xù)發(fā)展施加更多影響,并構建基于RISC-V發(fā)展標準的能力。

綜合來看,作為開源指令集,RISC-V技術本身基本不會受到技術封鎖的影響。 基于RISC-V完全開放和諸多授權免費的特性,隨著RISC-V平臺的進一步壯大和開放,對于國內外的芯片設計企業(yè)而言,不失為爭取更多開發(fā)自由和自主權的擇優(yōu)之選。

- 林芝地智能穿戴物聯(lián)卡行業(yè)綜合解決方案

- 林芝地安防監(jiān)控物聯(lián)卡行業(yè)綜合解決方案:智能化時代的“安全守護者”

- 林芝地物聯(lián)卡是如何盤活自動售貨機市場的?

- 林芝地車聯(lián)網物聯(lián)卡行業(yè)綜合解決方案:驅動智慧出行的“數字紐帶”

- 林芝地POS機物聯(lián)卡行業(yè)綜合解決方案:驅動智能支付場景的數字化轉型

- 林芝地智慧林業(yè):構建全鏈路數字化生態(tài)系統(tǒng)的創(chuàng)新實踐

- 林芝地智慧農業(yè):重塑現代農業(yè)的數字化革命?

- 林芝地智慧醫(yī)療:生命科學革命下的醫(yī)療生態(tài)重構

- 林芝地智慧城市綜合解決方案:構建未來城市的智慧引擎

- 林芝地智慧交通綜合解決方案